# 日本国特許庁

別紙添付の書類に記載されている事項は下記の出願書類に記載されている事項と同一であることを証明する。 This is to certify that the annexed is a true copy of the following application as filed with this Office.

出願年月日 Date of Application: 2002年12月 2日 出願番号 Application Number: [ST. 10/C]: [JP2002-350177]

> 特許庁長官 Commissioner, Japan Patent Office

出 願 <sup>人</sup> 大見 忠弘 Applicant(s):

2003年11月25日

特願2002-350177

| 【書類名】    | 特許願         |

|----------|-------------|

| 【整理番号】   | M-9928      |

| 【提出日】    | 平成14年12月 2日 |

| 【あて先】    | 特許庁長官殿      |

| 【国際特許分類】 | H01L 21/304 |

a.

# 【発明者】

【住所又は居所】 宮城県仙台市青葉区米ケ袋2丁目1番17号301【氏名】 大見 忠弘

【発明者】

【住所又は居所】 宮城県仙台市宮城野区平成1丁目1番地22号コーポ丹 野K6

# 【発明者】

【住所又は居所】 神奈川県横浜市旭区さちが丘148-4-701

【氏名】 赤堀 浩史

### 【発明者】

【住所又は居所】 宮城県仙台市太白区西の平1丁目23-45グラシアス C-203

【氏名】 二井 啓一

# 【特許出願人】

【識別番号】 000205041【氏名又は名称】 大見 忠弘

# 【代理人】

| 【識別番号】   | 10007 | 1272 |

|----------|-------|------|

| 【弁理士】    |       |      |

| 【氏名又は名称】 | 後藤    | 洋介   |

۶.

【選任した代理人】 【識別番号】 100077838 【弁理士】 【氏名又は名称】 池田 憲保 【手数料の表示】 【予納台帳番号】 012416 21,000円 【納付金額】 【提出物件の目録】 明細書 1 【物件名】 【物件名】 図面 1 【物件名】 要約書 1

۲

a.

【プルーフの要否】 要

【書類名】 明細書

【発明の名称】 半導体装置、その製造方法、及び、半導体表面の処理方法 【特許請求の範囲】

【請求項1】 実質的に(110)面方位をその表面に有するシリコンに半 導体素子が形成された半導体装置において、

その表面ラフネスが、中心線平均粗さRaで表現すると0.15nm以下であることを特徴とする半導体装置。

【請求項2】 実質的に(110)面方位をその表面に有するシリコンに半 導体素子が形成された半導体装置において、

その表面ラフネスが、中心線平均粗さRaで表現すると0.11nm以下であることを特徴とする半導体装置。

【請求項3】 実質的に(110)面方位をその表面に有するシリコンに半 導体素子が形成された半導体装置において、

その表面ラフネスが、中心線平均粗さRaで表現すると0.09nm以下であることを特徴とする半導体装置。

【請求項4】 実質的に(110)面方位をその表面に有するシリコンに半 導体素子が形成された半導体装置において、

その表面ラフネスが、中心線平均粗さRaで表現すると0.07nm以下であ ることを特徴とする半導体装置。

【請求項5】 請求項1乃至4のいずれかにおいて、前記Raは0.02n m以上であることを特徴とする半導体装置。

【請求項6】 請求項1乃至5のいずれかにおいて、前記実質的に(110) ) 面方位を有する表面は、(110)面、(551)面、(311)面、(22 1)面、(553)面、(335)面、(112)面、(113)面、(115) ) 面、(117)面、(331)面、(221)面、(332)面、(111) 面、及び、(320)面のいずれかであることを特徴とする半導体装置。

【請求項7】 請求項1乃至5のいずれかにおいて、前記実質的に(110) 面方位を有する表面は、(110) 面または(551) 面であることを特徴と する半導体装置。

【請求項8】 請求項1乃至7のいずれか一つにおいて、前記半導体装置は

ソース領域、ドレイン領域及びチャネル領域とを含む半導体表面と、

チャネル領域上に形成されたゲート絶縁膜と

ゲート絶縁膜上にゲート電極を有する電界効果トランジスタであることを特徴 とする半導体装置。

【請求項9】 請求項8において、前記電界効果トランジスタのゲート絶縁 膜は、シリコン酸化膜、シリコン窒化膜、シリコン酸窒化膜の何れか一つ以上を 含む膜によって構成されていることを特徴とする半導体装置。

【請求項10】 請求項8又は9において、前記ゲート絶縁膜中には、希ガ スが含まれていることを特徴とする半導体装置。

【請求項11】 請求項8乃至10のいずれかに記載された半導体装置において、前記電界効果トランジスタのゲート絶縁膜は、

Hf、Zr、Ta、Ti、La、Co、Y及びAlの一つ又は何れかの元素を 組み合わせた金属シリケイト、

Si、Hf、Zr、Ta、Ti、Y、Nb、Na、Co、Al、Zn、Pb、 Mg、Bi、La、Ce、Pr、Sm、Eu、Gd、Dy、Er、Sr及びBa から選ばれる一つ又は何れかの元素を組み合わせた金属酸化物、

Si、Hf、Zr、Ta、Ti、Y、Nb、Na、Co、Al、Zn、Pb、 Mg、Bi、La、Ce、Pr、Sm、Eu、Gd、Dy、Er、Sr及びBa から選ばれる一つ又は何れかの元素を組み合わせた金属窒化物、

あるいは、

Si、Hf、Zr、Ta、Tj、Y、Nb、Na、Co、Al、Zn、Pb、 Mg、Bi、La、Ce、Pr、Sm、Eu、Gd、Dy、Er、Sr及びBa から選ばれる一つ又は何れかの元素を組み合わせた金属酸窒化物、

を含んだ高誘電膜を有していることを特徴とする半導体装置。

【請求項12】 請求項11において、前記ゲート絶縁膜は、シリコン酸化 膜、シリコン窒化膜、シリコン酸窒化膜、及び、前記高誘電膜から選択された膜 を組み合わせた構造であることを特徴とする半導体装置。

ページ: 3/

【請求項13】 酸素ラジカルを含む雰囲気で、半導体領域の表面に犠牲酸 化膜を形成する工程と、

前記犠牲酸化膜を剥離する工程とを含み、これにより、半導体領域の表面平坦 性を向上させることを特徴とする半導体装置の製造方法。

【請求項14】 チャネル領域及びゲート絶縁膜を含む半導体装置を製造する方法において、

酸素ラジカルを含む雰囲気で、半導体表面に犠牲酸化膜を形成する工程と、

前記犠牲酸化膜を剥離する工程とにより、前記チャネル領域の半導体表面の平 坦性を向上させ、

当該平坦性を向上させたチャネル領域の半導体表面に、ゲート絶縁膜が形成されることを特徴とする半導体装置の製造方法。

【請求項15】 請求項13又は14に記載された半導体装置の製造方法に おいて、前記ラジカル酸素を含む雰囲気は、マイクロ波励起により発生させられ た希ガスと酸素ガスの混合ガスプラズマを用いて実現されることを特徴とする半 導体装置の製造方法。

【請求項16】 請求項15に記載された半導体装置の製造方法において、 前記希ガスはクリプトンまたはアルゴンであることを特徴とする、半導体装置の 製造方法。

【請求項17】 請求項15に記載された半導体装置の製造方法において、 前記ゲート絶緑膜を形成する工程は、ラジカル酸素、ラジカル窒素の少なくとも 一つを含む雰囲気中において、半導体表面を酸化処理する工程及び窒化処理する 工程の少なくとも一方、或いは、同時並行処理工程を含んでいることを特徴とす る、半導体装置の製造方法。

【請求項18】 請求項14に記載された半導体装置の製造方法において、 前記ゲート絶縁膜を形成する工程は、マイクロ波励起により発生させられた希ガ スと絶縁膜形成ガスの混合ガスプラズマを用いて前記ゲート絶縁膜を形成する工 程を含むことを特徴とする、半導体装置の製造方法。

【請求項19】 請求項18に記載された半導体装置の製造法において、前 記希ガスはクリプトンまたはアルゴンであり、前記絶縁膜形成ガスはアンモニア

、窒素、酸素の少なくとも一つ、或いは、それらの混合ガスであることを特徴と する、半導体装置の製造方法。

【請求項20】 シリコン表面に、湿式ガスを用いた酸化処理を行い、酸化 膜を形成する第1工程と、

前記酸化膜を剥離すること無く、10A以上1000A以下の厚さまでエッチ バックする第2工程と、

その後、第1工程と第2工程を所望数繰り返し、

最後にHFを含む水溶液により酸化膜を剥離することにより、シリコン表面を 平坦化することを特徴とする半導体装置の製造方法。

【請求項21】 オゾンを含有する純水による洗浄を行う第1工程、500 kHz以上の周波数の振動を与えながら、HFと、脱気したH2Oと、界面活性 剤とを含有する洗浄液による洗浄を行う第2工程、オゾンを含有するH2Oによ る洗浄を行う第3工程、酸化膜を除去するためにHFと脱気したH2Oを含有す る洗浄液による洗浄を行う第4工程、水素が添加されたH2Oによる洗浄を行う 第5工程とからなる洗浄方法を含むことを特徴とする半導体装置の製造方法。

【請求項22】 請求項21に記載された半導体装置の製造方法において、 前記第2及び第4工程の脱気したH<sub>2</sub>Oは、H<sub>2</sub>Oを脱気した後に水素を添加す ることによって形成されたH<sub>2</sub>Oであることを特徴とする半導体装置の製造方法 。

【請求項23】 HFと、溶存酸素濃度が100ppb以下のH<sub>2</sub>Oとを含 有する洗浄液により、シリコン酸化膜、シリコン窒化膜、シリコン酸窒化膜の少 なくとも一つを剥離処理することを特徴とする半導体装置の製造方法。

【請求項24】 500kHz以上の周波数の振動を与えながら、HFと、 溶存酸素濃度が100ppb以下のH2OへHを添加した洗浄液により、半導体 表面を洗浄することを特徴とする半導体装置の製造方法。

【請求項25】 請求項21乃至24のいずれかに記載された半導体装置の 製造方法において、半導体装置の洗浄開始から終了まで、処理薬液と半導体装置 が空気に触れることが無いような装置中で処理を行うことを特徴とする、半導体 装置の製造方法。

【請求項26】 半導体表面の処理方法において、

前記半導体表面を洗浄する工程と、

前記洗浄された半導体表面を平坦化する工程とを有することを特徴とする半導体表面の処理方法。

【請求項27】 請求項26において、前記半導体表面は、実質的に(110)の面方位を有するシリコン表面であることを特徴とする半導体表面の処理方法。

【請求項28】 請求項27において、前記表面を平坦化する工程は、中心 線平均粗さ(Ra)で前記半導体表面を0.15nmより小さくする工程である ことを特徴とする半導体表面の処理方法。

【請求項29】 請求項28において、前記表面を平坦化する工程は、

酸素ラジカルを含む雰囲気で前記半導体表面に犠牲酸化膜を形成する工程と、

前記犠牲酸化膜を剥離する工程とを有していることを特徴とする半導体表面の 処理方法。

【請求項30】 請求項26乃至29のいずれかにおいて、前記洗浄する工 程は、

OH濃度の低いRCA洗浄工程であることを特徴とする半導体表面の処理方法。

【請求項31】 請求項26乃至29のいずれかにおいて、半導体表面を処理する液体のpHを7以下にしたことを特徴とする半導体表面の処理方法。

【請求項32】 請求項31において、前記洗浄する工程は、 OHの発生を抑制した超音波洗浄を含むことを特徴とする半導体表面の処理方法。

【請求項33】 半導体表面のラフネスを平坦化する半導体表面の処理方法 において、

前記半導体表面を湿式酸化によって酸化し、酸化膜を形成する第1の工程と、

前記酸化膜を所定の厚さまでエッチバックする第2の工程とを有し、

更に、前記第1及び第2の工程を少なくとも2回繰り返した後、第2の工程で 残された残膜を剥離する工程を含み、これによって、前記半導体表面を平坦化す

ることを特徴とする半導体表面の処理方法。

【請求項34】 半導体表面のラフネスを維持する半導体表面の処理方法に おいて、

前記半導体表面をオゾンを含有する純水によって洗浄する第1工程、500k Hz以上の周波数の振動を与えながら、HFと、脱気したH2Oと、界面活性剤 とを含有する洗浄液による洗浄を行う第2工程、オゾンを含有するH2Oによる 洗浄を行う第3工程、酸化膜を除去するためにHFと脱気したH2Oを含有する 洗浄液による洗浄を行う第4工程、水素が添加されたH2Oによる洗浄を行う第 5工程とを含み、これによって、前記半導体表面の表面を維持することを特徴と する半導体表面の処理方法。

【請求項35】 請求項34に記載された半導体表面の処理方法において、 前記第2及び第4工程の脱気したH2Oは、H2Oを脱気した後に水素を添加す ることによって形成されたH2Oであることを特徴とする半導体表面の処理方法。

【請求項36】 HFと、溶存酸素濃度が100ppb以下のH<sub>2</sub>Oとを含 有する洗浄液により、シリコン酸化膜、シリコン窒化膜、シリコン酸窒化膜のい ずれか一つを剥離処理することを特徴とする半導体表面の処理方法。

【請求項37】 500kHz以上の周波数の振動を与えながら、HFと、 溶存酸素濃度が100ppb以下のH2OへHを添加した洗浄液により、半導体 表面を洗浄することを特徴とする半導体表面の処理方法。

【請求項38】 請求項34乃至37のいずれかに記載された半導体表面の 処理方法において、半導体表面の洗浄開始から終了まで、処理薬液と半導体表面 が空気に触れることが無いような装置中で処理を行うことを特徴とする半導体表 面の処理方法。

【発明の詳細な説明】

[0001]

【発明の属する技術分野】

本発明は、改善された移動度等の特性を有する半導体装置及びその製造方法、 並びに、半導体表面の処理方法に関する。 [0002]

【従来の技術】

Ľ

一般に、この種の半導体装置には、シリコン等の半導体表面にそってソース領 域、ドレイン領域、及び、チャネル領域を形成した電界効果トランジスタがある 。更に、この電界効果トランジスタは、チャネル領域上に形成されたゲート絶縁 膜、及び、ゲート絶縁膜上にゲート電極を有している。良く知られているように 、電界効果トランジスタには、n型電界効果トランジスタ(n型トランジスタ) とp型電界効果トランジスタ(p型トランジスタ)とがあり、これらn型とp型 トランジスタを含むLSIを作成する場合、表面に(100)面を有するシリコ ン(以下、(100)シリコンと呼ぶ)が使用されるのが普通である。尚、本明 細書における面方位の記述として、例えば、(100)は、(100)面と等価 な面(100)、(010)、(001)等、全てを総称して表しているものと する。

[0003]

このように、(100)シリコンを用いて、n型トランジスタ及びp型トラン ジスタを形成した場合、p型トランジスタの駆動能力、例えば、移動度が、n型 トランジスタに比較して、約0.3倍程度低くなることが知られている。このた め、通常、p型トランジスタのサイズをn型トランジスタのサイズに比較して大 きく設計する手法が採用されている。しかしながら、p型トランジスタのサイズ をn型トランジスタのサイズよりも大きく設計することは、微細化を妨げる要因 の一つともなっている。

[0004]

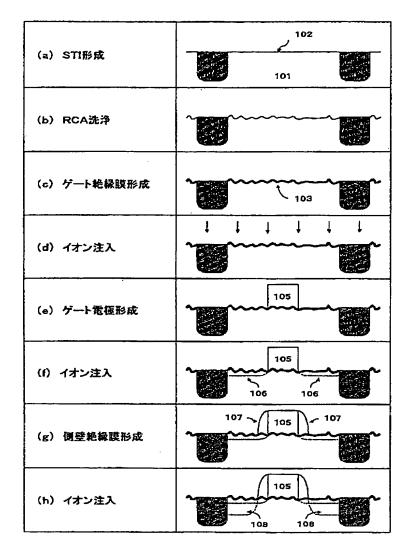

ここで、図1を参照して、半導体領域にn型トランジスタを形成し、集積回路 を構成する場合を例にとって、従来の半導体装置の製造方法を説明する。尚、こ の例は、LDD(Lightly Doped Drain)構造のn型トラン ジスタを製造する工程を示している。

[0005]

まず、図1 (a) に示すように、p型(100) シリコン101の表面に、例 えば、STI (Shallow Trench Isolation) 法により

素子分離を行い、素子領域102が形成される。ここで、シリコンの面方位(100)には、(100)面に等価な面(100)、(010)、(001)が含まれることは前述した通りであり、この場合、(100)の表面を有するシリコンは、半導体基板、或いは、半導体基板上に形成された半導体層であっても良い。

[0006]

次に、素子領域102に対して、NH<sub>4</sub>OH-H<sub>2</sub>O<sub>2</sub>-H<sub>2</sub>O(SC1)及 びHC1-H<sub>2</sub>O<sub>2</sub>-H<sub>2</sub>O(SC2)を用いたRCA洗浄が行われる(図1( b))。RCA洗浄後、有機物、パーティクル、メタル不純物が全表面から除去 された後、ゲート絶縁膜(SiO<sub>2</sub>)103が形成される(図1(c))。

[0007]

更に、図1(d)に示すように、シリコン101の全面に、閾値電圧を制御す るため、ボロンがイオン注入される。イオン注入後、シリコン101の全面に、 多結晶シリコン膜が堆積され、これをパターニングすることにより、素子領域1 02のゲート絶縁膜103上に、多結晶シリコン電極105が図1(e)に示す ように形成される。

[0008]

続いて、図1(f)に示すように、リンを低濃度でイオン注入することにより、高電界を緩和するn-ソース及びn-ドレイン領域106が形成される。次に、CVD法などにより、ゲート電極105を被覆するように、シリコン酸化膜(SiO<sub>2</sub>)を、シリコン101の全面に堆積させ、異方性エッチングを行って、ゲート電極105の側壁に側壁絶縁膜107を形成する(図1(g))。その後、砥素などのn型不純物を高濃度にイオン注入してn+ソース及びドレイン領域108を形成する(図1(h))。

【0009】

(100)シリコンを使用して、図示された方法により作成されたn型トラン ジスタは、前述したように、p型トランジスタに比較して移動度において低いと 言う欠点がある。

[0010]

一方、p型トランジスタの駆動能力を高めるために、表面に(110)面を有 する(110)シリコンを使用することが提唱されている。実際、(110)シ リコンを使用した場合、p型トランジスタの駆動能力は、(100)シリコンを 使用した場合に比較して、約2.5倍にも上昇することが報告されている。しか しながら、(110)シリコンを使用した場合、逆に、n型トランジスタの駆動 能力が約0.6倍程度、(100)シリコンを使用した場合より低下してしまう 。したがって、n型トランジスタの駆動能力の低下を抑えることができれば、( 110)シリコンは、非常に有用な材料となる。しかしながら、(110)シリ コンを使用して、n型トランジスタの駆動能力の低下を防止する方法については 、未だ提案されていないのが実情である。

[0011]

また、(110)シリコンにも適用できると考えられる装置及び方法が、特願 平9-15790号(特表平10-33362号公報)(引用文献1)及び特開 平11-57636号公報(引用文献2)においてそれぞれ開示されている。し かしながら、引用文献1は、(100)シリコンのみを用いて行ったものであり 、(110)シリコンについては、実験はなされていなかったものである。同様 に、引用文献2は、(100)シリコンを用いた場合の実験結果であり、(11 0)シリコンについては、実験は行われていない。

[0012]

一方、特開平9-51097号公報(引用文献3)は、シリコンと酸化膜との 間の界面における電子散乱による界面移動度の劣化を回避できる電界効果トラン ジスタの製造方法を開示している。しかしながら、引用文献3は(001)シリ コンにおける電子の走行方向とスップの方向とを平行にすることを開示している だけで、(110)シリコンについては検討していない。

[0013]

【特許文献1】

特表平10-33362号公報

[0014]

【特許文献2】

特開平11-57636号公報

[0015]

【特許文献3】

特開平9-51097号公報

[0016]

【発明が解決しようとする課題】

本発明者等の観察によれば、図1に示されたような方法により、電界効果トラ ンジスタを製造した場合、RCA洗浄におけるアルカリ処理時、並びに、純水リ ンス時等に、素子領域表面が不可避的に粗面化してしまうことが判明した。

[0017]

一方、電界効果トランジスタにおけるキャリアの移動度は、当該トランジスタ の駆動能力を示す指標の一つであり、p型電界効果トランジスタにおいてはホー ル、n型電界効果トランジスタにおいては電子がそれぞれキャリアとなる。一般 的に、電界効果トランジスタの駆動能力を向上させるためには、素子領域の表面 の粗さを少なくしてキャリアの移動度を上げる必要がある。

[0018]

具体的に説明すると、通常のRCA洗浄を用いた場合、素子領域におけるシリ コンの表面ラフネスは、中心線平均粗さRaで表現すると、Ra=0.5~1. 5nm程度の荒れを生じ、その上に、ゲート絶縁膜が形成されることを本発明者 等は確認した。ゲート絶縁膜形成にはドライO2を用いて形成されるSiO2膜 が一般であるが、ドライO2を用いる酸化の場合、(111)ファセット面から 酸化種が進入し、優先的に酸化が進むと考えられ、その結果、シリコン表面とゲ ートSiO2膜界面の粗さは、更に大きくなることが観測された。

[0019]

RCA洗浄による微小な荒れを有するシリコンを用いて、電界効果トランジス タを作製した場合、当該電界効果トランジスタの駆動能力が低下するのみならず 、実際にゲート電極に電圧を加えた場合、突起部に電界集中が生じ、絶縁破壊に 至りやすくなる。特に、実質的に(110)面方位をその表面に有するシリコン を用いた場合、アルカリ処理時における荒れは激しくなり、このことが、当該実

質的(110)面方位をその表面に有するシリコンを用いた場合における移動度 の低下等を招く。

[0020]

以上、n型電界効果トランジスタを例にとって説明したが、TFT、CCDや IGBT等の半導体素子についても、同様なことが言える。

[0021]

本発明は、このような事情によりなされたものであり、その目的はシリコン表 面の粗さを低減させることにより、改善された性能を有する半導体装置を提供す ることである。

[0022]

本発明の他の目的は、実質的に(110)面方位をその表面に有するシリコン を用いて高い表面平坦性を有し、特性の向上した半導体装置を提供することであ る。

[0023]

本発明の別の目的は、実質的に(110)面方位をその表面に有するシリコン を使用して、駆動能力の高いn型トランジスタを製造する製造方法を提供するこ とである。

[0024]

本発明の更に他の目的は、半導体領域表面の粗さを小さくすることができる半 導体装置の製造方法を提供することである。

[0025]

本発明の他の目的は、洗浄によって生じる半導体領域表面の粗さを維持又は平 坦化することができる半導体表面の処理方法を提供することである。

[0026]

【課題を解決するための手段】

本発明は、実質的に(110)面方位をその表面に有するシリコンの表面ラフ ネスを、中心線平均粗さRaで、Ra=0.15nm以下とすることで、半導体 装置におけるキャリア電子の散乱を低く抑え、半導体装置のキャリア電子駆動能 力を向上させることに特徴がある。半導体装置のキャリア電子移動度は、半導体 領域表面のラフネスと密接な関係を持ち、特に、実質的に(110)面方位をその表面に有するシリコンでは、Raを小さくするに従い、キャリア電子の移動度 を向上させることが可能となる。

[0027]

ここで、実質的な(110)面方位とは、結晶学的に見て、(110)面方位

とほぼ等価な方向を向いている面であり、(551)面、(311)面、(22

1)面、(553)面、(335)面、(112)面、(113)面、(115))面、(117)面などを含んでいる。

[0028]

Kazuo Sato等によれば、"Sensors and Actuat ors 73 (1999)" (P122—130)に掲載された論文のFig . 2に、 (110)面をアルカリエツチング処理した場合、<-110>方向に 筋が走る表面形状となることが示されている。このように、 (110)面と同様 な表面形状が得られる領域として、<100>方向に0~12°までオフさせた 面、例えば、8°オフの (551)面などが当てはまる。<-110>方向へは 1°オフさせた面までは、同様な表面形状が得られる。したがって、当該論文の Fig. 2に示された (110)面と同じ表面ラフネス挙動を示す面方位は、実 質的に (110)面方位に含まれる。

[0029]

更に、T. Sato等は、Phys. Rev., B4, 1950 (1971) において、(110)面と同様なキャリア電子移動度が得られる面を報告してい る。この報告によれば、<-110>方向に電子を流した場合、<-110>方 向 $<0~35^{\circ}$ オフさせた面、例えば(331)面、(221)面、(332) 面、(111)面などを用いても(110)面と同様の電子移動挙動を得ること が出来る。また、<110>方向 $<0~12^{\circ}$ オフさせた面、例えば(320) 面を用いても(110)面と同様の挙動を得ることが出来る。したがって、上記 した面やその近傍面も、本明細書で言う実質的(110)面に含まれる。

[0030]

上記した点を前提として、以下本発明の特徴を列挙する。まず、本発明の半導

体装置は、実質的に(110)面方位をその表面に有するシリコンに半導体素子 が形成された半導体装置において、その表面ラフネスが、中心線平均粗さRaで 表現すると0.15nm以下、好ましくは0.11nm以下であることを特徴と している。更に、前記Raは0.09nm以下が望ましく、0.07nm以下が 更に好ましい。

[0031]

前記半導体装置は、電界効果トランジスタであっても良い。

[0032]

前記電界効果トランジスタのゲート絶縁膜は、シリコン酸化膜、シリコン窒化 膜、シリコン酸窒化膜の何れか一つ以上を含む膜であっても良い。

[0033]

前記電界効果トランジスタのゲート絶縁膜中には、希ガスを含んでも良い。

[0034]

前記電界効果トランジスタのゲート絶縁膜には、

Hf、Zr、Ta、Ti、La、Co、Y及びAlの一つ又は何れかの元素を 組み合わせた金属シリケイト、

Si、Hf、Zr、Ta、Ti、Y、Nb、Na、Co、Al、Zn、Pb、 Mg、Bi、La、Ce、Pr、Sm、Eu、Gd、Dy、Er、Sr及びBa から選ばれる一つ又は何れかの元素を組み合わせた金属酸化物、

Si、Hf、Zr、Ta、Ti、Y、Nb、Na、Co、Al、Zn、Pb、 Mg、Bi、La、Ce、Pr、Sm、Eu、Gd、Dy、Er、Sr及びBa から選ばれる一つ又は何れかの元素を組み合わせた金属窒化物、

あるいは、

Si、Hf、Zr、Ta、Ti、Y、Nb、Na、Co、Al、Zn、Pb、 Mg、Bi、La、Ce、Pr、Sm、Eu、Gd、Dy、Er、Sr及びBa から一つ又は何れかの元素を組み合わせた金属酸窒化物

を含んだ高誘電膜で形成しても良い。

【0035】

前記電界効果トランジスタのゲート絶縁膜は、シリコン酸化膜、シリコン窒化

膜、シリコン酸窒化膜、または高誘電膜、これら何れかの膜を組み合わせた構造 であっても良い。

[0036]

本発明の一態様に係る半導体装置の製造方法は、半導体領域の表面平坦性を向 上させるため、酸素ラジカルを含む雰囲気で、半導体領域の表面に犠牲酸化膜を 形成する工程と、前記犠牲酸化膜を剥離する工程とを含むことを特徴としている 。

[0037]

前記ラジカル酸素を含む雰囲気は、マイクロ波励起により発生させられた希ガスと酸素ガスの混合ガスプラズマを用いて実現しても良い。

[0038]

本発明の別の態様に係る電界効果トランジスタの製造方法は、チャネル領域を 形成するにあたり、チャネル領域の半導体表面の平坦性を向上させるため、酸素 ラジカルを含む雰囲気で半導体表面に犠牲酸化膜を形成する工程と、前記犠牲酸 化膜を剥離する工程と、チャネル領域の半導体表面にゲート絶縁膜を形成する工 程とを有することを特徴としている。

[0039]

前記ラジカル酸素を含む雰囲気は、マイクロ波励起により発生させられた希ガ スと酸素ガスの混合ガスプラズマを用いて実現しても良い。

[0040]

前記希ガスは、クリプトンまたはアルゴンであっても良い。

[0041]

前記ゲート絶縁膜は、ラジカル酸素、ラジカル窒素の少なくとも一つを含む雰 囲気中において、半導体表面を酸化処理、窒化処理の何れか乃至は同時並行処理 を含むことで形成しても良い。

[0042]

前記ゲート絶縁膜は、マイクロ波励起により発生させられた希ガスと絶縁膜形 成ガスの混合ガスプラズマを用いて形成しても良い。

[0043]

前記希ガスはクリプトンまたはアルゴンであり、絶縁膜形成ガスはアンモニア 、窒素、酸素の何れか乃至はそれらの混合ガスであっても良い。

[0044]

本発明の他の態様に係る半導体装置の製造方法又は半導体表面の処理方法は、 シリコン表面に湿式ガスを用いた酸化処理を行う第1工程と、酸化膜を剥離する こと無く10A以上1000A以下までエッチバックする第2の工程と、その後 、第1工程と第2の工程を所望数繰り返し、最後にHFを含む水溶液により酸化 膜を剥離することにより、シリコン表面を平坦化することを特徴としている。

[0045]

本発明の別の態様による半導体装置の製造方法又は半導体表面処理方法は、 p Hが7以下の非アルカリ性の液体のみで半導体を処理または半導体表面の洗浄を 行うことを含んでいる。

[0046]

前記洗浄方法は、超音波洗浄をOHの発生を抑制しつつ行っても良い。

[0047]

前記〇日の発生の抑制は、H2を添加することによって行っても良い。

[0048]

本発明の別の態様に係る半導体装置の製造方法又は半導体表面の処理方法は、 オゾンを含有する純水による洗浄を行う第1工程、500kHz以上の周波数の 振動を与えながら、HFと、脱気したH2Oと、界面活性剤とを含有する洗浄液 による洗浄を行う第2工程、オゾンを含有するH2Oによる戦場をおこなう第3 工程、酸化膜を除去するためにHFと脱気したH2Oを含有する洗浄液による洗 浄を行う第4工程、水素が添加されたH2Oによる洗浄を行う第5工程、からな る洗浄方法を含んでいる。

[0049]

前記第2、第4工程の脱気したH<sub>2</sub>Oは、H<sub>2</sub>Oを脱気した後に水素を添加したH<sub>2</sub>Oを用いても良い。

[0050]

前記洗浄方法は、洗浄開始から終了まで、処理薬液と半導体装置が空気に触れ

ることが無くても良い。

[0051]

本発明の更に他の態様に係る半導体装置の製造方法、又は、半導体表面の処理 方法は、HFと、溶存酸素濃度が100ppb以下のH2Oとを含有する洗浄液 により、シリコン酸化膜、シリコン窒化膜、シリコン酸窒化膜の剥離処理を行う ことを特徴としている。

[0052]

前記剥離処理は、剥離開始から終了まで、処理薬液と半導体装置が空気に触れることが無くても良い。

[0053]

本発明の別の態様に係る半導体装置の製造方法、又は、半導体表面の処理方法 は、500kHz以上の周波数の振動を与えながら、HFと、溶存酸素濃度が1 00ppb以下のH2OへHを添加した洗浄液により、半導体表面を洗浄するこ とを特徴としている。

[0054]

前記洗浄処理は、洗浄開始から終了まで、処理薬液と半導体装置が空気に触れることが無くても良い。

[0055]

【発明の実施の形態】

<u>本発明の原理</u>:

以下では、(110)シリコンを使用して電界効果トランジスタを構成した場合について説明する。まず、(110)シリコン表面におけるキャリア電子の移動度を、律速する要因(律速要因)について説明すると、移動度の律速要因として、通常、①不純物散乱 $\mu_{co}$ 、②ホノン散乱 $\mu_{ph}$ 、③表面ラフネス散乱 $\mu_{s}$ rの3つの要因が挙げられる。更に、観測される移動度 $\mu$ は、3つの要因の足し合わせとなっており、Mattersonの法則で与えられ、下記の数1式によってあらわされることが知られている。

[0056]

$$\mu^{-1} = \mu_{\rm co}^{-1} + \mu_{\rm ph}^{-1} + \mu_{\rm sr}^{-1}$$

[0057]

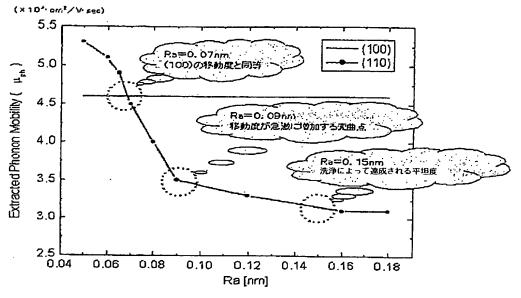

上記した3つの律速要因の中で、(110)面における電子キャリアが、シリ コン表面のラフネス(即ち、表面ラフネス散乱 $\mu_{sr}$ )に大きく影響を受けるこ とが判明した。実際に、極低温にて移動度と実効電界との関係を調べると、不純 物散乱 $\mu_{co}$ 及びホノン散乱 $\mu_{ph}$ を実質的に無視することができ、表面ラフネ ス散乱 $\mu_{sr}$ による影響だけを抽出することが出来る。そこで、77kにて移動 度と実効電界との関係を調べた結果、(110)面は、(100)面よりも、界 面ラフネスが移動度に与える影響が大きいことが分かった。

【0058】

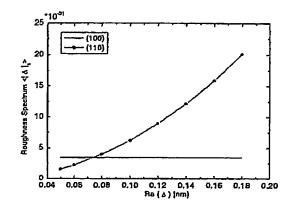

更に、図2を参照すると、中心線平均組さRaと界面ラフネススペクトルとの 関係を、シミュレーションにより調べた結果が示されている。従来手法を用いて 実際に実現可能なRaが約0.4 nmであることを考慮すると、図2に示された 中心線平均組さRaと界面ラフネススペクトルとの関係は、従来手法による限界 より小さいRa領域における関係であることが分かる。ここで、界面ラフネスス ペクトルとは、物理的に測定などで求められるラフネスではなく、実際にキャリ アが感じているラフネスであり、以下の数2式のように定義する。

[0059]

【数2】

$$\langle |\Delta_{q}|^{2} \rangle = \pi \Delta^{2} \Lambda^{2} e^{\left(-\frac{q^{2} \Lambda^{2}}{4}\right)}$$

[0060]

ここで、 $\Delta$ は、界面ラフネスの中心線平均粗さRa、Aは、界面ラフネスの平 均周期であり、更に、qは、キャリアの界面への入射波数ベクトルkと反射波数 ベクトルk'との差(即ち、q=k-k')である。

[0061]

図2に示すように、(100)面では、Raの変化に対して、界面スペクトル の変化は無視できるほど小さい。それに対して、(110)面の場合、Ra低下 に従い、ラフネススペクトルは低下し、キャリアの移動度が上昇することが分か る。更に、図2からも明らかな通り、Raを0.07nm以下にすることで、( 100)シリコンにおける電子移動度と同等レベルまで、(110)シリコンに おける移動度が向上することがシミュレーションにより推測できる。

[0062]

そこで、本発明の趣旨は(110)シリコン表面のRaを従来の限界である0.4 nm以下、特に、0.15 nm以下、好ましくは、0.07 nm以下まで平坦 化できる手法及び平坦化されたシリコンを用いて形成された半導体装置を得ることにある。

[0063]

<u>第1の実施形態</u>:

図3を参照して、本発明の第1の実施形態に係る半導体装置の製造方法を説明 する。

[0064]

まず、図3(a)に示すように、p型(110)シリコン301を用意し、そ の表面に、例えばSTI(Shallow Trench Isolation) )法により素子分離を行い、ソースドレイン及びチャネル領域を含む素子領域3 02を形成する。

[0065]

次に、素子領域302に対し、有機物、パーティクル、メタル汚染除去の為、 RCA洗浄を施す(図3(b))。また、本発明にように、微細な粗さ(ラフネ ス)が問題となるようなラフネス領域では、RCA洗浄の一工程であるSC1洗 浄時におけるラフネスの増加をも考慮しておく必要があることが分かった。実際 、RCA洗浄の一工程であるSC1洗浄時に、OH濃度によってシリコン表面が エッチングされ、当該エッチングによりラフネスが増加することが確認された。

[0066]

このことを考慮して、この実施形態では、OH濃度が低いSC1洗浄処理を施

す。典型的な従来のSC1処理では、NH<sub>4</sub>OH:H<sub>2</sub>O<sub>2</sub>:H<sub>2</sub>O=1:1: 5の薬液が使用される。しかしながら、本発明の第1の実施形態では、NH<sub>4</sub>O H:H<sub>2</sub>O<sub>2</sub>:H<sub>2</sub>O=0.05:1:5と、従来のSC1処理に比較してOH 濃度を下げている。

[0067]

尚、シリコン結晶中において、COP(Crystal Originate d Particle)等の欠陥密度が高い場合、SC1処理時に表面ラフネス の増加が加速することも観測された。更に、欠陥が原因で、SC1処理後にマイ クロピットが表面に形成され、酸化膜耐圧の劣化も誘発することが判明した。特 に、CZウェハを用いた場合、COP密度が高いことが知られている。

[0068]

従って、SC1洗浄時における表面ラフネスの増加を抑制するには、好ましく は、シリコン表面に水素アニール処理、または、アルゴンアニール処理等を施し 、残留酸素のレベルを、5E16/cm3程度まで低下させたシリコンを用いる か、さらにはSiエピタキシャル成長を表面に施したシリコンウェハを用いるの が良い。本実施形態では、Siエピタキシャル成長を表面に施したシリコンウェ ハを用いた。

[0069]

このように、前記低OH濃度のSC1工程を用いた場合、シリコン表面は、0 .15nm程度の中心線平均粗さRaを有していた。この程度の表面粗さを有す るシリコンを用いてn型トランジスタを作製した場合、従来のn型トランジスタ に比較して改善された移動度を有するn型トランジスタを得ることができる。し かしながら、図2からも明らかな通り、(110)シリコンを使用した場合、こ の程度のRaでは、(100)シリコンを使用した場合と同等の移動度は達成で きない。

[0070]

そこで、この実施形態では、表面粗さを更に平坦化するために、図3(c)に 示すように、素子領域のシリコン表面の平坦化処理として、ラジカル酸素を含む 雰囲気中において、素子領域表面を酸化し、犠牲酸化膜303を形成する。この

ラジカル酸素雰囲気で犠牲酸化膜303を形成することによって、当該犠牲酸化 膜303の表面は犠牲酸化膜303の形成前に比較して平坦化されることが確認 された。

[0071]

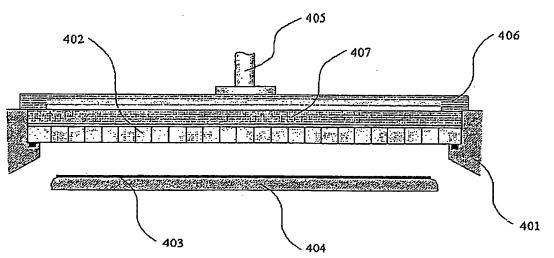

ここで、図3(c)で使用したラジカル酸化ついて、図4を参照して具体的に 説明する。

[0072]

図4には、本発明のラジカル酸化処理を行うために使用したラジアルラインス ロットアンテナを用いた装置の一例が示されている。図示された装置は、特許願 9-133422(特表平10-33362号公報参照)に開示されたプラズマ 装置と実質的に同等の構成を備え、本発明では、当該装置を用いて、シリコン酸 化膜は次のようにして形成される。

[0073]

図4において、真空チャンバー401は、まず、真空状態にされ、続いて、シャワープレート402からKrガス、O2ガスを導入し、処理室内の圧力を1T orr程度に設定する。一方、(110)面方位のシリコン403が加熱機構を 持つ試料台404に置かれ、試料の温度が400℃程度になるように設定されて いる。この温度設定を200~550℃の範囲内で変化させても、以下に述べる 結果と殆ど同様の結果が得られる。

[0074]

同軸導波管405から、ラジアルラインスロットアンテナ406、誘電体板4 07を通して、処理窒内に、2.45GHzのマイクロ波を供給し、処理室内に 高密度のプラズマを生成する。また、供給するマイクロ波の周波数は、900M Hz以上10GHz以下の範囲であれば以下に述べる結果はほとんど同様のもの と成る。シャワープレート402とシリコン403の間隔は、本実施例では6c mにしている。この間隔は狭い方がより高速な酸化が可能となる。本実施形態で は、ラジアルラインスロットアンテナを用いたプラズマ装置を用いて酸化した例 を示したが、他の方法を用いてマイクロ波を処理室内に導入しても良い。

[0075]

ラジカル酸素を含む雰囲気中でシリコン表面を酸化する場合、シリコン表面の 突起部分への酸化種の付着確率が高い効果と、さらには、ラジカルが突起部に当 ると、突起部が負に帯電し、O+やO2+等の酸素イオンを引き寄せ易くなる効 果が相乗し、突起部分が優先的に酸化され、結果として、シリコン表面には、平 坦化されたシリコン酸化膜が形成されるものと推測される。

[0076]

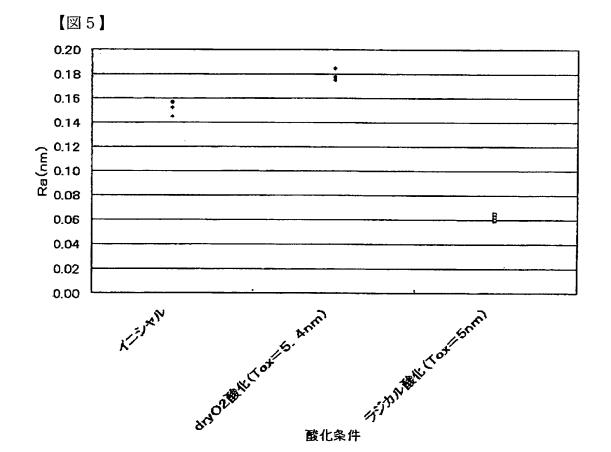

図5には、ドライ酸化をシリコン表面に施した場合と、ラジカル酸素を含む雰 囲気中で酸化を施した場合で、酸化前後における表面平坦変化の様子が示されて いる。ここで、イニシャルは、前記低OH濃度のSC1工程を行った後の中心線 平均粗さRaが示されており、図からも明らかな通り、Raは0.14~0.16 の範囲にある。

[0077]

このようなシリコン表面に、ドライ酸化により、シリコン酸化膜を形成した場 合、Raは0.17~0.19nmとの間に変化している。一方、本発明のように 、ラジカル酸化によりシリコン酸化膜を形成した場合、その表面のRaは0.0 7nmよりも小さくなっている。このように、ドライ酸化の場合は、酸化により ラフネスが増加しているのに対し、ラジカル酸化を施すことにより、平坦性が向 上していることが分かる。

[0078]

図5に示された酸化後のラフネスは、酸化膜をHFとHC1混合液(体積比率、HF:HC1=1.19)に1分間浸して剥離した後のものである。尚、エッ チングにHFとHCIの混合液を用いたのは、なるべく低OHイオン濃度の薬液 を用いることにより、絶縁膜剥離時におけるシリコン表面のエッチングを抑制し 、シリコンとゲート絶縁膜界面の状況を正確に把握する為である。酸化後のラフ ネスを測定する前に、(110)シリコンを、HFとHC1の混合液に10分以 上浸潰した後、浸漬前後でのRaの変化を調べた。この結果、浸漬前後において 、(110)シリコンにRaの変化が認められず、シリコンのエッチングは生じ ないことが確認できた。このことにより、本評価手法の妥当性が確認出来た。以 降、絶縁膜下のシリコン表面のラフネス値は、前記HFとHC1の混合液に1分

間浸して絶縁膜を剥離した後に評価した値とする。

[0079]

前述したように、ラジカル酸化を施した場合、表面の平坦性を向上させること ができる。本ラジカル酸化処理を用いたシリコン表面の平坦化は、シリコン面方 位や適応される半導体素子に限定されること無く、他の半導体素子にも応用が可 能な技術である。

$\begin{bmatrix} 0 & 0 & 8 & 0 \end{bmatrix}$

図3(d)に示すように、前述した犠牲酸化膜303の形成(図3(c))後、当該犠牲酸化膜303の剥離が行われる。本実施形態では、HF:HC1=1 :19の体積比で混合したpHが1以下の薬液を使用して、犠牲酸化膜303を 剥離した。

[0081]

次に、図3(e)に示すように、ラジカル酸素を含む雰囲気中で素子領域のシ リコン表面を酸化し、5nmのゲート絶縁膜(SiO2)304を形成する。こ の状態で、シリコンを、HF:HCI=1:19の体積比で混合したpHが1以 下の薬液に1分間浸漬を用いて、ゲート絶縁膜を剥離し、シリコン表面とゲート 絶縁眼の界面ラフネスを評価したところ、中心線平均粗さRaで、0.06nm が達成できた。

[0082]

尚、本発明において形成されるシリコン酸化膜は、少なくともシリコンと接す る部分に存在すればよく、その上層に異種の材料、アルカリ土類金属、希土類金 属、遷移金属を用いた酸化物、窒化物、酸窒化物、シリケートなどが1層以上積 層形成された絶縁膜を用いても良い。また、本発明において形成されるシリコン 酸化膜の代わりに、アルカリ土類金属、希土類金属、遷移金属を用いた酸化物、 窒化物、酸窒化物、シリケートなどの単層または積層構造を用いても良い。更に は、シリコン酸化膜、シリコン窒化膜、シリコン酸窒化膜の何れか一つ以上を含 む膜を用いても良い。ここで、本発明においてゲート絶縁膜として使用できる高 誘電膜を構成する材料を例示すると、Hf、Zr、Ta、Ti、La、Co、Y 及びA1の一つ又は何れかの元素を組み合わせた金属シリケイト、Si、Hf、

Zr、Ta、Ti、Y、Nb、Na、Co、Al、Zn、Pb、Mg、Bi、L a、Ce、Pr、Sm、Eu、Gd、Dy、Er、Sr及びBaから選ばれる一 つ又は何れかの元素を組み合わせた金属酸化物、Si、Hf、Zr、Ta、Ti 、Y、Nb、Na、Co、Al、Zn、Pb、Mg、Bi、La、Ce、Pr、 Sm、Eu、Gd、Dy、Er、Sr及びBaから選ばれる一つ又は何れかの元 素を組み合わせた金属窒化物、あるいは、Si、Hf、Zr、Ta、Ti、Y、 Nb、Na、Co、Al、Zn、Pb、Mg、Bi、La、Ce、Pr、Sm、 Eu、Gd、Dy、Er、Sr及びBaから一つ又は何れかの元素を組み合わせ た金属酸窒化物が含まれる。

[0083]

図3(f)に戻ると、シリコン301の全面に、閾値電圧を制御するため、ボ ロンがイオン注入される。ボロンのイオン注入後、シリコン301の全面に、多 結晶シリコン膜を堆積させ、これをパターニングして素子領域302のゲート絶 縁膜304上に、多結晶シリコン電極(ゲート電極)305を形成する(図3( g))。

[0084]

次に、リンを低濃度でイオン注入して高電界を緩和する n – ソース及び n – ド レイン領域306を形成する(図3(h))。

[0085]

次に、CVD法などにより、ゲート電極305を被覆するように、シリコン酸 化膜(SiO<sub>2</sub>)を、シリコン301の全面に堆積させた後、異方性エッチング を行って、ゲート電極305の側壁に側壁絶縁膜307を形成する(図3(i))。

[0086]

その後、砥素などのn型不純物を高濃度にイオン注入してn+ソース及びn+ ドレイン領域308を形成し、n型トランジスタが得られた(図3(j))。

[0087]

次に、図3(b)に示されたRCA洗浄後におけるRaと移動度との関係を検 討した。ここでは、RCA洗浄後退のSC1洗浄時のアンモニア濃度を変化させ

ることにより、シリコン表面の中心線平均粗さRaを、0.05~0.18nm と変化させ、その際における移動度のラフネス散乱成分の変化を調べた。

[0088]

図6には、その結果が図6に示されている。図6より、Raが低下するに従い 、移動度は向上することが分かる。前記した低OH濃度のSC1工程を用いた場 合、Raは0.15nm程度であり、それが洗浄によって達成できる平坦限界と 言える。これ対して、本発明の第1の実施形態のように、ラジカル酸化により犠 牲酸化膜を形成し、それを剥離する工程を入れることで、Raを0.05nmま で平坦化が達成出来た。

[0089]

図6に示された(110)シリコンのRaと移動度との関係からも明らかなよ うに、Raを0.15nm以下とすることで、電子移動度の向上現象を確認出来 た。また、Raを0.09nm以下にすると、急激に移動度が増加することが分 かった。0.09nmは急激な移動度上昇が起こり始める変曲点と言える。更に 、Raを0.07nmまで平坦化することで、(100)表面で得られるキャリ ア電子移動度と同等の移動度が得られ、移動度は0.05nm以下まで改善され ることが予測できる。

[0090]

以上は、洗浄後、前記ラジカル犠牲酸化を行うことにより、非常に平坦な面を 得ることが出来たことで、初めて得ることが出来た知見である。

[0091]

図6からも明らかな通り、第1の実施形態では、Ra=0.05nmを達成で きており、従来技術と比較し、n型トランジスタの移動度を、1.6倍向上させ ることが実現できた。

[0092]

さらに従来技術より、シリコン表面とゲート絶縁膜との界面が平坦であることか ら、ゲート絶縁膜の信頼性も向上させることが出来る。

[0093]

以上の(110)シリコン表面におけるキャリア電子移動度の向上については

、電界効果トランジスタのみならず、広く、TFT、CCDやIGBT等の半導 体素子についても、容易に応用が可能である。

[0094]

第2の実施形態:

次に、図7を参照して、第2の実施形態に係る半導体装置の製造方法を説明す る。

[0095]

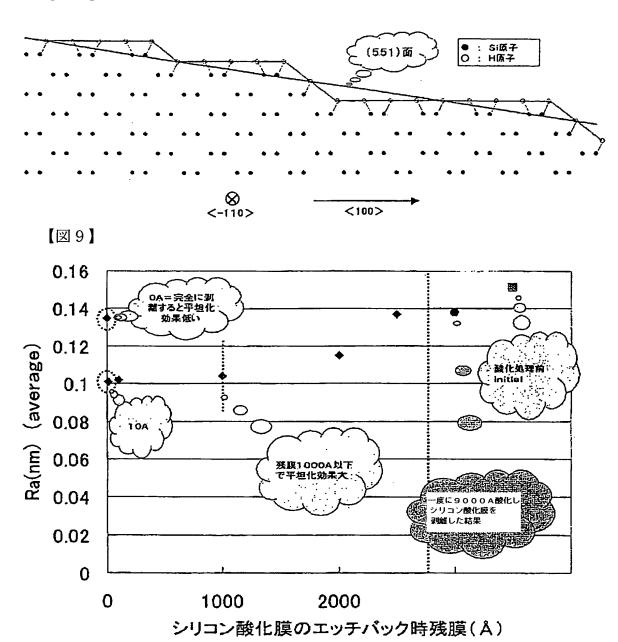

第1の実施形態では、表面にSiエピタキシャル成長処理を施した(110) シリコン面を用いたが、第2の実施形態では、表面にSiエピタキシヤル成長処 理を施した(110)シリコン面を、<100>方向へ8°オフさせたシリコン 面を用い、更に、シリコン酸窒化膜を用いた場合について述べる。尚、前述の8 \*オフさせた面は、(551)シリコン面と言い換えることが出来る。

[0096]

図7(a)に示すように、p型(551)シリコン701の表面に、例えば、 STI(Shallow Trench Isolation)法により素子分 離が施され、ソースドレイン及びチャネル領域を含む素子領域702が形成され る。

[0097]

次に、図7(b)に示すように、素子領域702に対し、有機物、パーティク ル、メタル汚染除去の為、RCA洗浄が施される。尚、第1の実施形態と同様に 、SC1時におけるラフネス増加を抑制するために、NH4OH:H2O2:H 2O=0.05:1:5と、OH濃度を下げた薬液を使用した。

[0098]

その後、図7(c)及び(d)のように、素子領域のシリコン表面の平坦化処 理として、300℃~500℃のラジカル酸素を含む雰囲気中で、素子領域表面 に犠牲酸化膜703を形成し、更に、前記犠牲酸化膜を剥離する。本実施形態で は、犠牲酸化膜剥離に、HF:HCl=1:19の体積比で混合したpHが1以 下の薬液を使用した。その時点での表面状況を観察すると、図8に示すように、 (110)面が表面に現れたテラスと、<-110>方向に沿ったステップによ

り、自己整合的に、階段状の形状が現れる。ステップの高さは0.17~0.3 5 nm程度、中心線平均粗さRaで0.04 nm程度が好ましい。

[0099]

次に、図7(e)に示すように、ラジカル酸素を含む雰囲気で素子領域のシリ コン表面を酸化し、ゲート絶縁膜(酸窒化膜)704を形成する。この状態で、 ゲート絶縁膜を、HF:HCl=1:19の体積比で混合したpHが1以下の薬 液に浸漬して剥離し、シリコン表面とゲート絶縁膜の界面ラフネスを評価したと ころ、中心線平均粗さRaで、0.05nmが達成できた。尚、比較の為に、ラ ジカル犠牲酸化処理を行わなかったシリコン表面の中心線平均粗さRaを調べた ところ、0.15nmであった。

[0100]

本発明の電界効果トランジスタのゲートシリコン酸窒化膜は、第1の実施形態 と同様に、ラジアルラインスロットアンテナを用いたマイクロ波励起プラズマ処 置(図4)を使用することによって形成できる。具体的には、シリコン酸窒化膜 は次のようにして形成される。まず、図4に示された真空チャンバー401内を 真空にし、シャワープレート402からKrガス、O2ガス、NH3ガスを導入 し、処理室内の圧力を1 Torr程度に設定する。一方、加熱機構を持つ試料 台404には、(110)面方位のシリコン403を置き、試料の温度が400 ℃程度になるように設定する。この温度設定は200~550℃の範囲内で以下 に述べる結果はほとんど同様のものとなる。

[0101]

この状態で、同軸導波管405から、ラジアルラインスロットアンテナ406 、誘電体板407を通して、処理室内に、2.45GHzのマイクロ波を供給し 、処理室内に高密度のプラズマを生成する。シャワープレート402とシリコン 403の間隔は、本実施形態では6cmにしている。本実施形態の説明は、ラジ アルラインスロットアンテナを用いたプラズマ装置を用いて酸化した例を示した が、他の方法を用いてマイクロ波を処理室内に導入しても良い。

[0102]

本発明のシリコン酸窒化膜形成においては、水素が存在することがひとつの重

要な要件である。プラズマ中に水素が存在することにより、シリコン酸窒化膜中 及び界面のダングリングボンドがSi-H、N-H結合を形成して終端され、そ の結果、シリコン酸窒化膜及び界面の電子トラップが無くなる。Si-H結合、 N-H結合が本発明の酸窒化膜に存在することは、それぞれF11R、XPSを 測定することで確認されている。水素が存在することで、CV特性のヒステリシ スも無くなり、シリコンとシリコン酸窒化膜界面密度も3×1010cm-2と 低く抑えられる。希ガス(ArまたはKr)とO2、N2、H2の混合ガスを使 用してシリコン酸窒化膜を形成する場合には、水素ガスの分圧を0.5%以上と することで、膜中の電子や正孔のトラップが急激に減少することが判明した。

[0103]

本発明において、マイクロ波励起プラズマ処理室内に導入するガスを、例えば、Krガス、NH3ガスとすることで、シリコン窒化膜を形成することも可能となる。

[0104]

更に、本発明において形成されるシリコン酸窒化膜またはシリコン窒化膜は、 少なくともシリコンと接する部分に存在すればよく、その上層に異種の材料、ア ルカリ土類金属、希土類金属、遷移金属を用いた酸化物、窒化物、酸窒化物、シ リケートなどが1層以上積層形成された絶縁膜を用いても良い。また本発明にお いて形成されるシリコン酸窒化膜の代わりに、アルカリ土類金属、希土類金属、 遷移金属を用いた酸化物、窒化物、酸窒化物、シリケートなどの単層または積層 構造を用いても良い。

[0105]

図7に戻ると、前述したゲート絶縁膜形成後、シリコン701の全面に、しき い値電圧を制御するため、ボロンをイオン注入する(図7(f))。

[0106]

続いて、シリコン701の全面に、多結晶シリコン膜を堆積させ、これをパタ ーニングして、図7(g)に示すように、素子領域フ702のゲート絶縁膜70 3上に、多結晶シリコン電極705をゲート電極として形成する。次に、図7( h)に示すように、リンを低濃度でイオン注入して高電界を緩和するn-ソース 及びドレイン領域706を形成する。

[0107]

更に、CVD法などにより、ゲート電極4を被覆するように、シリコン酸化膜 (SiO<sub>2</sub>)を、シリコン701の全面に堆積させた後、異方性エッチングを行 って、図7(i)に示すように、ゲート電極705の側壁に側壁絶縁膜707を 形成する。

[0108]

その後、砥素などのn型不純物を高濃度にイオン注入してn+ソース及びドレイン領域708を形成し、n型トランジスタが得られた(図7(j))。

[0109]

上記した本発明の第2の実施形態に係る製造方法で作製された電界効果トラン ジスタのキャリア電子移動度を評価した結果、従来技術と比較し、移動度を1. 6倍向上させることが実現できた。

[0110]

更に、従来技術より、シリコン表面とゲート絶縁膜との界面が平坦であること から、ゲート絶縁膜の信頼性も向上させることが出来る。

[0111]

以上、シリコン表面をラジカル犠牲酸化処理によって平坦化した場合の実施形 態を示したが、ラジカル犠牲酸化処理以外の手法を用いても、平坦性を維持また は向上させることができる。

[0112]

<u>第3の実施形態</u>:

まず、湿式酸化を用いた平坦性向上の実施形態を第3の実施形態として説明する。

[0113]

比較的大きいラフネスを有する表面を備えた(110)シリコンを用意し、1 000℃、H<sub>2</sub>=1slm、O<sub>2</sub>=1slmの条件で、当該シリコン表面を湿式 酸化し、シリコン酸化膜3000Aを形成する(第1工程)。次に、HFを含む H<sub>2</sub>O薬液により、シリコン酸化膜を残膜厚0~2500Aとなるまでエッチバ ックを行い(第2工程)、その後、第1工程と第2工程を、2回繰り返し、最後 にHF:HC1=1:19の体積比で混合したpHが1以下の薬液を用いシリコ ン酸化膜を完全に剥離した。

[0114]

その結果を図9に示す。図9の横軸は、第2工程におけるシリコン酸化膜の残 膜量(厚さ)を示し、縦軸は中心線平均粗さRaを示している。リファレンスと して、一度に9000Aのシリコン酸化膜を形成し、HF:HC1=1:19の 体積比で混合したpHが1以下の薬液を用いてシリコン酸化膜を剥離したものを 示す。

[0115]

この結果、第2工程におけるエッチバック時の残膜厚を小さくするに従い、R aは低減することが分かり、残膜厚1000Aでほぼ飽和している。しかしなが ら、残膜0、つまり、シリコン酸化膜を全て剥離し切ってしまうと、平坦化の効 果が失われる。

[0116]

これは、薬液処理によりシリコン面が露出すると、薬液自身によるシリコン表 面のアタックやメタル汚染付着などの平坦化を阻害する要因が増加することに起 因するものと推測される。また、第2工程における残膜量を適切な値、例えば、 残膜100Aなどにすれば、一度に9000Aのシリコン酸化膜を形成し剥離す るよりも、第1工程と第2工程を繰り返した処理を行った方が、平坦化効果が高 いことが確認出来た。

[0117]

酸化とエッチバックによる平坦化効果のメカニズムは不明であるが、エッチバ ックにより残膜を薄くすると、シリコンとシリコン酸化膜界面付近に、湿式酸化 時の酸化種が均一に届きやすくなることも一因と推測される。

[0118]

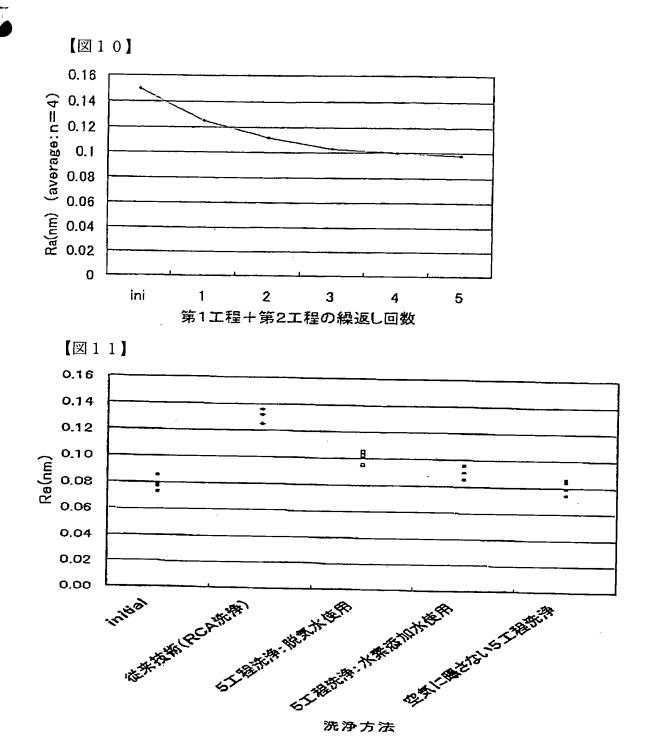

更に、第1工程と第2工程の繰り返し回数と平坦性との関係を調べ、その結果 を図10に示す。図10の横軸は、繰り返し回数、縦軸は中心線平均粗さRaで ある。図10からも明らかな通り、繰り返し3回を超えると、ほぼ飽和の傾向が 見られ、繰り返し回数には適正値があることが確認出来た。

[0119]

以上より、湿式ガスを用いた酸化を行い(第1工程)、酸化膜を剥離すること 無く10A以上1000A以下までエッチバックを行い(第2工程)、その後、 第1工程と第2工程を所望数繰り返し、最後にHFを含む水溶液により酸化膜を 剥離することによっても、シリコン表面をイニシャルウェハに比較して平坦化す ることが出来る。

[0120]

第4の実施形態:

次に、薬液処理を用いて平坦性維持及び改善する手法を本発明の第4の実施形 態として説明する。シリコン表面の洗浄にはRCA洗浄が多用されていることは 前述した通りであるが、RCA洗浄工程のSC1洗浄(80℃程度に昇温させた アンモニアと過酸化水素水と純水液中にシリコンを浸漬しての洗浄)中に、Si -Si結合の弱い部分がOHイオンによりアタックされ、Si表面が荒れること が知られている。SC1処理では、過酸化水素水によるシリコン表面の酸化と、 OHイオンによるSi-Oエッチング、さらにはSi-Siエッチングによるエ ッチバックを同時に進行させる。そのことにより、パーティクル除去や有機物汚 染除去の効果が高いという特徴を有するものの、Si表面を荒らすという副作用 が存在する。シリコン表面をなるべく荒らさない為には、アルカリ洗浄を無くし た洗浄処理方法が求められる。アルカリ洗浄処理を無くし、RCAと同等レベル 以上のパーティクル除去、有機汚染除去、メタル汚染除去能力を有する洗浄方法 として、特開平11-057636号公報に、5つの工程を用いた洗净処理方法 が示されている。

[0121]

当該公報に示された洗浄方法は、オゾンを含有する純水による洗浄を行う第1 工程、500kHz以上の周波数の振動を与えながら、HFとH2Oと界面活性 剤とを含有する洗浄液による洗浄を行う第2工程、オゾンを含有する純水による 洗浄を行う第3工程、シリコン酸化膜を除去する為のHFとH2Oを含有する洗 浄液による洗浄を行う第4工程、純水による洗浄を行う第5工程からなることを 特徴としている。

[0122]

特開平11-057636号公報に示された洗浄方法は、前述のようにアルカ リ処理が入っていないことから、Si表面の平坦性を損なうことなく洗浄を行う ことができるものと推測され、当該公報には、洗浄前又は後の表面がRaで0. 11nmに保たれている例が示されている。しかしながら、当該公報には、RC A洗浄を施した場合、表面ラフネス(Ra)が荒れると言う事実について指摘し ていない。更に、当該公報は、本発明者等の一部による実験結果を示しており、 (100)面方位をその表面に有するシリコンに限って行った実験結果である。 (110)面方位をその表面に有するシリコンの場合、イニシャルウェハーが0. 15nm以下のものは得られないし、同方法を用いても0.15nm以下のRa は得られない。

[0123]

本発明者等は、前述した第1~第5の工程のうち、第2工程及び第4の工程に 用いるH<sub>2</sub>Oを脱気させ、溶存酸素量を下げる処理を施すことによって、表面の 平坦性を維持できることを見出した。ここでは、この方法を本発明の第4の実施 形態として説明すると、当該第4の実施形態における第2工程では、第1工程に おいて形成されたシリコン酸化膜を除去し、パーティクルの除去を行っている。 同じく、第4工程においては、第3工程において形成されたシリコン酸化膜を除 去し、メタル汚染の除去を行っている。

(0124)

第2及び第4の工程において、薬液中に溶存酸素が存在すると、HFにより除 去されたSi表面において、Si-Si結合の弱い部分が選択的に再酸化され、 更に、HFにより除去されることが同時に進行し、結果、表面ラフネスが増大し てしまう。そこで、第4の実施形態では、第2および第4の工程における溶存酸 素量を従来のppmオーダーから100ppb以下(好ましくは、10ppb以 下)まで下げ、薬液処理を行った結果、表面ラフネス(Ra)を維持できること を見出した。

[0125]

より具体的に説明すると、(110)シリコンに対しオゾン5ppm含む純水 による洗浄を5分行い(第1工程)、950kHzの周波数の振動を与えながら 、脱気した0.5%HF水と、脱気したH2Oと、50ppmの界面活性剤とを 含有する洗浄液による洗浄を5分行った(第2工程)。次に、オゾンを5ppm 含有する純水による洗浄を5分行い(第3工程)、酸化膜を除去する為の脱気し た0.5%HFと脱気したH2Oを含有する洗浄液による洗浄を1分行い(第4 工程)、脱気したH2OにHを0.1~50ppm添加した超純水による洗浄を 10分行った(第5工程)。

[0126]

また、洗浄は、シリコンを洗浄液に浸漬する事で行った。洗浄が終了したシリ コン表面のラフネスを、従来のRCAと比較した結果を図11に示す。図11か らも明らかな通り、洗浄前にRaが0.08nmのシリコン表面に、従来技術の RCA洗浄を施すと、0.13nmまで粗くなるが、本発明の実施形態では、0 .10nmと荒れが緩和していることが分かる。

[0127]

尚、本発明のように、シリコン酸化膜を剥離する際に、HFと、100ppb 以下の溶存酸素濃度を有するH2Oとを含有する洗浄液を用いることで、シリコ ン表面の荒れを緩和することが出来る技術は、(110)シリコンのみならず、 他の面方位にも応用が可能である。更に、本発明はシリコン窒化膜、シリコン酸 窒化膜のいずれか一つを剥離処理を行う際にも利用できる。

[0128]

また、第2工程及び第4工程に用いるH<sub>2</sub>Oを脱気させ、その後、水素を0. 1~50ppm添加することで、溶存酸素量を下げる効果に加え、OHイオン濃度を下げることを試み、RCAと比較した結果も図11に示す。この結果、Ra は、イニシャルウェハーの0.08nmと比較し、0.01nm程度、荒れるも のの、その程度は低減出来ていることが分かる。特に、第2工程においては、従 来技術だと、500kHz以上の周波数の振動を与えながら処理すると、H<sub>2</sub>O がHとOHに解離し、OH濃度が上昇すると言う間題があった。本発明では、H Fに、脱気することで溶存酸素が100ppb以下とした後にHを50ppm添 加したH2Oと、50ppmの界面活性剤とを含有する洗浄液による洗浄を行う ことにより、Raを実質的に維持できる。このことは、OHの発生を抑制した超 音波洗浄が第2工程で行われていることを意味している。尚、溶存酸素は10p pb以下が好ましい。

[0129]

更に、第2工程及び第4工程に用いるH2Oを脱気させ、その後、水素を0. 1~50ppm添加した薬液を使用することに加え、5つの工程を処理するにあ たり、洗浄開始から終了まで、洗浄薬液とシリコン表面共に空気に晒すことの無 い装置内で処理することで、空気中から薬液へ酸素が溶け込むことを防止した。 従来のRCAと比較した結果をも図11に示す。図からも明らかな通り、イニシ ャルウェハーの0.08nmと比較して荒れは生じず、表面ラフネス(Ra)を 維持できることが分かる。

[0130]

前述した半導体の処理或いは洗浄は、pHが7以下の非アルカリ性の液体のみ で行われても良い。この場合、超音波洗浄をOHの発生を抑制しつつ行っても良 いし、OH発生の抑制はH2を添加することによって行っても良い。

[0131]

【発明の効果】

本発明によれば、ラジカル酸素を含む雰囲気で平坦化処理を行なうことで、シ リコン表面の平坦性を、従来のRCA洗浄によって得られる1.0nm程度の表 面ラフネス(Ra)を0.05nmまで低下させることが出来たし、0.02n mまでも充分可能と思われる。この結果、実質的に(110)面方位をその表面 に有するシリコンにおいて、そのキヤリア電子移動度を、従来技術より1.6倍 向上させることが出来、(100)面方位における移動度と同等以上にすること が出来る。さらに、シリコン表面とゲート絶縁膜界面が原子的に平坦であること から、ゲート綺縁膜の信頼性も向上する。

【図面の簡単な説明】

【図1】

従来技術における電界効果トランジスタの製造工程を説明する工程図である。

【図2】

シリコン表面の中心線平均粗さRaと界面ラフネススペクトルとの関係を調べ たシミュレーション結果を示すグラフである。

【図3】

本発明の第1の実施形態に係る電界効果トランジスタの製造工程を示す工程図 である。

【図4】

図3の製造工程で使用される装置の概略構成を示す断面図である。

【図5】

本発明の第1の実施形態に係る製造方法による効果を説明するグラフであり、 ここでは、シリコン表面の平坦化に対する酸化方法の依存性を示している。

【図6】

シリコン表面の中心線平均組さRaと電子移動度との関係を説明するグラフで ある。

【図7】

本発明の第2の実施形態に係る電界効果トランジスタの製造方法を説明する工 程図である。

【図8】

図7に示された製造方法で使用される(551)面における原子ステップの模 式図である。

【図9】

本発明の第3の実施形態に係る製造方法の第2工程におけるシリコン酸化膜の エッチバツク残膜量とRaとの関係を示すグラフである。

【図10】

本発明の第3の実施形態で行われる第1工程と第2工程の繰り返し回数とRa との関係を示す図である。

【図11】

0

本発明の第4の実施形態に係る表面平坦性維持手法の効果を示すグラフである

"4

•

1

:

...

| 【符号の説明】 |                |

|---------|----------------|

| 301、701 | p 型(1 1 0)シリコン |

| 302,702 | 素子領域           |

| 303、703 | 犠牲酸化膜          |

| 304,704 | ゲート絶縁膜         |

| 305、705 | ゲート電極          |

| 306,706 | n-ソース、ドレイン領域   |

| 307、707 | 側壁絶縁膜          |

| 308,708 | n+ソース、ドレイン領域   |

.

...

【図1】

2

:

【図3】

:

1

•

4

| (a) STI形成   | 302            |

|-------------|----------------|

| (b)改良RCA洗浄  |                |

| (c) 平坦化酸化处理 | 309            |

| (d) 酸化酸剂酶処理 |                |

| (e)ゲート紀縁膜形成 | 304            |

| (1) イオン注入   |                |

| (g)ゲート電極形成  | 305            |

| (h) イオン注入   | 305<br>3D6 306 |

| (i) 例壁枪輪跋彩成 | 307 305 307    |

| (j) イオン注入   | 305<br>308 308 |

:

【図7】

:

| (=) stible   | 702         |

|--------------|-------------|

| (b) 社员RCA洗疗  |             |

| (c) 平坦化酸化丸理  | 703         |

| (8) 黃化資利加速   |             |

| (*) ゲート美谷政部成 | 704         |

| (1) イオン注入    |             |

| (2)ゲート重任計成   | 703         |

| (h) イオンエス    | 705         |

| (i) 何望他释这形成  | 707 705 707 |

| () イオンスス     | 705         |

|              |             |

【図8】

特願2002-350177

a

.

٠

【書類名】 要約書

【要約】

【課題】 通常のRCA洗浄では、中心線平均粗さで1.0 nm以上の表面粗さ が半導体表面に発生してしまい、このことが、(110)シリコンを用いたn型 トランジスタの特性を改善できない原因となっていた。

【解決手段】 (110)シリコンのような半導体表面をRaで0.15nm以 下にすることにより、移動度の高いトランジスタの作製を可能にする。具体的に は、RCA洗浄後の半導体表面に、ラジカル酸化によって酸化膜を形成した後、 この酸化膜を剥離することにより、平坦化された半導体表面が得られた。同様な 結果は、湿式酸化によって酸化膜を形成し、エッチバックを繰り返すことによっ ても得られた。

【選択図】 図3

特願2002-350177

# 出願人履歴情報

# 識別番号

٦

. .

- [000205041]

- 2. 変更年月日

1. 変更年月日

1. 変更年月日

1. 変更年月日

1. 変更年月日

1. 第規登録

住所

宮城県仙台市青葉区米ケ袋2-1-17-301

氏名

大見忠弘